Training

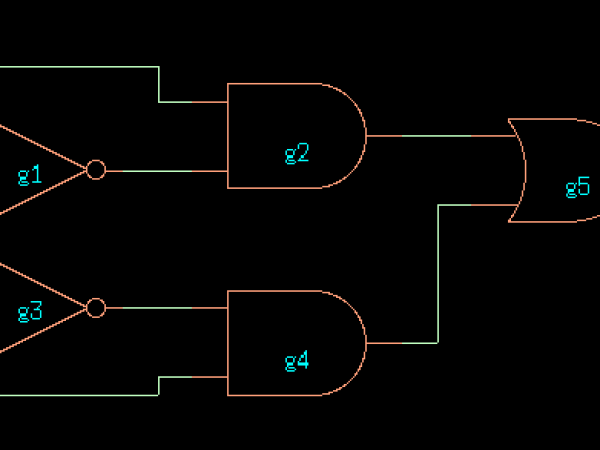

Design and Verification

This course provides in-depth knowledge of digital design and functional verification methodologies, focusing on RTL design and simulation.

Topics Covered:

- Digital design fundamentals (combinational & sequential logic)

- Verilog/SystemVerilog for RTL coding

- Testbench architecture

- UVM methodology

- Assertion-based verification

- Coverage-driven verification

- Simulation and debugging techniques

- Formal verification

- Industry-standard EDA tools

Design for Testability (DFT)

This course covers DFT techniques used in ASIC and SoC design, ensuring testability and high fault coverage.

Topics Covered:

- Basics of DFT and test methodologies

- Scan insertion (scan-based testing)

- Automatic Test Pattern Generation (ATPG)

- Built-in Self-Test (BIST) techniques

- JTAG (IEEE 1149.x standard)

- Memory BIST and Logic BIST

- Fault simulation and diagnosis

- Practical implementation using industry tools

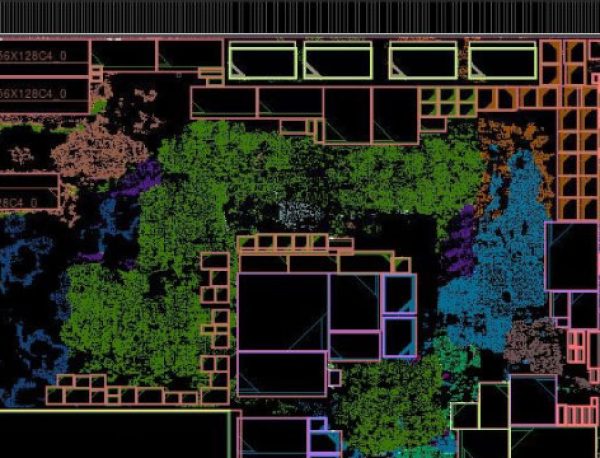

Synthesis

This course focuses on logic synthesis, transforming RTL into gate-level netlists while ensuring design constraints are met.

Topics Covered:

- RTL-to-gate-level transformation

- Constraints development (SDC)

- Timing-driven synthesis

- Design optimization techniques

- Power optimization strategies

- Clock gating and multi-clock domain considerations

- Static timing analysis (preliminary)

- Hands-on experience with industry tools

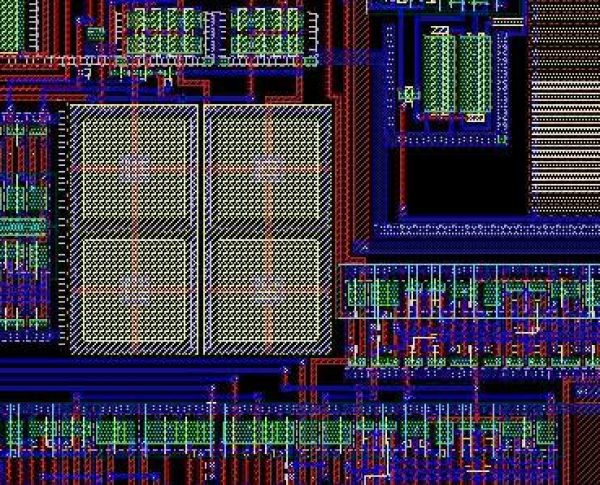

Place and Route (P&R)

This course provides an understanding of backend physical design, from floorplanning to final layout generation.

Topics Covered:

- Floorplanning and power planning

- Placement strategies

- Clock Tree Synthesis (CTS)

- Routing techniques

- Design for manufacturability (DFM) considerations

- Optimization for timing, power, and area

- Physical verification overview

- Tool-based implementation

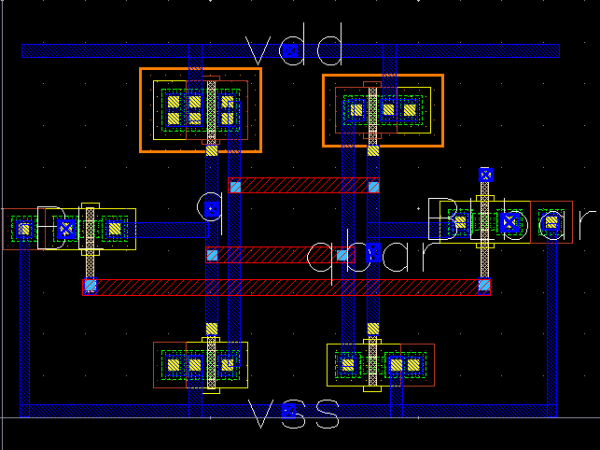

Physical Verification

This course covers the critical steps in physical verification to ensure design manufacturability and correctness.

Topics Covered:

- Layout vs. Schematic (LVS)

- Design Rule Checking (DRC)

- Parasitic Extraction (PEX)

- Antenna effect checking

- Metal density analysis

- Electrical rule checking (ERC)

- Foundry rules and compliance

- Industry-standard tools for verification

Static Timing Analysis (STA)

This course explains the process of analyzing and verifying circuit timing for high-performance chip design.

Topics Covered:

- Basics of timing analysis

- Timing constraints and formats (SDC)

- Setup and hold time analysis

- Clock domain crossing (CDC)

- Multi-mode, multi-corner analysis

- SI-aware STA (cross talk, noise)

- Debugging timing violations

- STA tools and implementation